Μετατροπέας αναλογικού σε ψηφιακό - σκοπός, ταξινόμηση και αρχή λειτουργίας

Μια ηλεκτρονική συσκευή που ονομάζεται μετατροπέας αναλογικού σε ψηφιακό (ADC) χρησιμοποιείται για τη μετατροπή ενός αναλογικού σήματος σε ψηφιακό σήμα (σε μια αναγνώσιμη ακολουθία τύπου δυαδικού κώδικα). Στη διαδικασία μετατροπής ενός αναλογικού σήματος σε ψηφιακό, υλοποιούνται τα εξής: δειγματοληψία, κβαντοποίηση και κωδικοποίηση.

Ως δειγματοληψία νοείται η λήψη δειγμάτων από ένα χρονικά συνεχές αναλογικό σήμα μεμονωμένων (διακριτών) τιμών που πέφτουν σε χρονικές στιγμές που σχετίζονται με ορισμένα διαστήματα και διάρκειες σημάτων ρολογιού που διαδέχονται το ένα το άλλο.

Η κβαντοποίηση περιλαμβάνει τη στρογγυλοποίηση της τιμής ενός αναλογικού σήματος που επιλέγεται κατά τη δειγματοληψία στο πλησιέστερο επίπεδο κβαντοποίησης, και τα επίπεδα κβαντοποίησης έχουν τον δικό τους αριθμό σειράς και αυτά τα επίπεδα διαφέρουν μεταξύ τους κατά μια σταθερή τιμή δέλτα, που δεν είναι τίποτα άλλο από βήμα κβαντοποίησης.

Αυστηρά μιλώντας, η δειγματοληψία είναι η διαδικασία αναπαράστασης μιας συνεχούς συνάρτησης ως μια σειρά από διακριτές τιμές και η κβαντοποίηση είναι η διαίρεση ενός σήματος (τιμών) σε επίπεδα. Όσον αφορά την κωδικοποίηση, εδώ η κωδικοποίηση νοείται ως σύγκριση των στοιχείων που λαμβάνονται ως αποτέλεσμα της κβαντοποίησης με έναν προκαθορισμένο συνδυασμό κωδικών.

Υπάρχουν πολλές μέθοδοι μετατροπής της τάσης σε κώδικα. Επιπλέον, κάθε μία από τις μεθόδους έχει μεμονωμένα χαρακτηριστικά: ακρίβεια, ταχύτητα, πολυπλοκότητα. Ανάλογα με τον τύπο της μεθόδου μετατροπής, τα ADC ταξινομούνται σε τρία

-

παράλληλα

-

σταθερός,

-

σειριακός-παράλληλος.

Για κάθε μέθοδο, η διαδικασία μετατροπής ενός σήματος με την πάροδο του χρόνου προχωρά με τον δικό της τρόπο, εξ ου και το όνομα. Οι διαφορές έγκεινται στον τρόπο με τον οποίο εκτελούνται η κβαντοποίηση και η κωδικοποίηση: μια σειριακή, παράλληλη ή σειριακή-παράλληλη διαδικασία για την προσέγγιση ενός ψηφιακού αποτελέσματος στο μετατρεπόμενο σήμα.

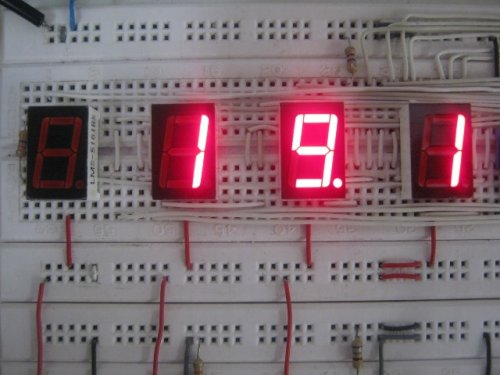

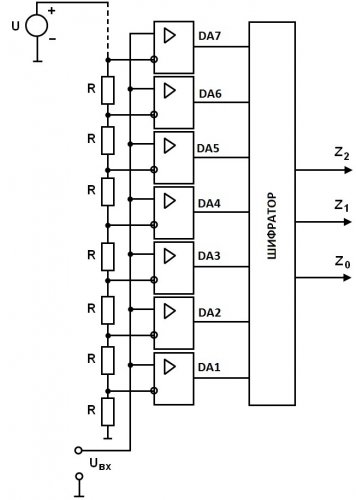

Το διάγραμμα ενός παράλληλου μετατροπέα αναλογικού σε ψηφιακό φαίνεται στο σχήμα. Οι παράλληλοι ADC είναι οι ταχύτεροι μετατροπείς αναλογικού σε ψηφιακό.

Ο αριθμός των ηλεκτρονικών συσκευών σύγκρισης (ο συνολικός αριθμός των συγκριτών DA) αντιστοιχεί στη χωρητικότητα του ADC: τρεις συγκριτές αρκούν για δύο bit, επτά για τρία, 15 για τέσσερα κ.λπ. Ο διαιρέτης τάσης αντίστασης έχει σχεδιαστεί για να ρυθμίζει ένα εύρος σταθερών τάσεων αναφοράς.

Η τάση εισόδου (η τιμή αυτής της τάσης εισόδου μετράται εδώ) εφαρμόζεται ταυτόχρονα στις εισόδους όλων των συγκριτών και συγκρίνεται με όλες τις τάσεις αναφοράς εκείνων που επιτρέπει να ληφθούν αυτός ο ωμικός διαιρέτης.

Αυτοί οι συγκριτές των οποίων οι μη αντιστρεφόμενες είσοδοι τροφοδοτούνται με τάση μεγαλύτερη από την αναφορά (που εφαρμόζεται από τον διαιρέτη στην αναστρέφουσα είσοδο) θα δώσουν μια λογική στην έξοδο, ενώ οι υπόλοιπες (όπου η τάση εισόδου είναι μικρότερη από την αναφορά ή ίση με μηδέν) θα δώσει μηδέν.

Στη συνέχεια συνδέεται ένας κωδικοποιητής, ο στόχος του είναι να μετατρέψει έναν συνδυασμό μονάδων και μηδενικών σε έναν τυπικό, επαρκώς κατανοητό δυαδικό κώδικα.

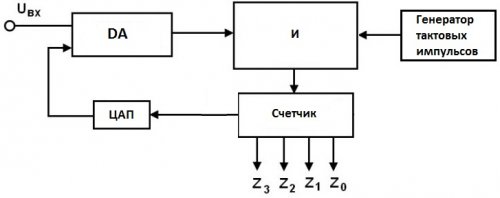

Τα κυκλώματα ADC για σειριακή μετατροπή είναι λιγότερο γρήγορα από τα κυκλώματα παράλληλων μετατροπέων, αλλά έχουν απλούστερο στοιχειώδες σχέδιο.Χρησιμοποιεί έναν συγκριτή, AND λογική, ένα ρολόι, έναν μετρητή και έναν μετατροπέα ψηφιακού σε αναλογικό.

Το σχήμα δείχνει ένα διάγραμμα ενός τέτοιου ADC. Για παράδειγμα, ενώ η μετρούμενη τάση που εφαρμόζεται στην είσοδο του κυκλώματος σύγκρισης είναι υψηλότερη από το σήμα ράμπας της δεύτερης εισόδου (αναφορά), ο μετρητής μετρά τους παλμούς της γεννήτριας ρολογιού. Αποδεικνύεται ότι η μετρούμενη τάση είναι ανάλογη με τον αριθμό των παλμών που μετρήθηκαν.

Υπάρχουν επίσης σειριακά παράλληλα ADC, όπου η διαδικασία μετατροπής ενός αναλογικού σήματος σε ψηφιακό σήμα διαχωρίζεται στο χώρο, έτσι αποδεικνύεται ότι η μέγιστη ταχύτητα ανταλλαγής επιτυγχάνεται με ελάχιστη πολυπλοκότητα.